Journal of Physical Sciences, Vol. 22, 2017, 163-173 ISSN: 2350-0352 (print), <u>www.vidyasagar.ac.in/journal</u> Published on 25 December 2017

# A New Method of Realization of Four-Quadrant Analog Multiplier using Operational Amplifiers and MOSFETs

Suvajit Roy, Tapas Kumar Paul, and Radha Raman Pal

Department of Physics and Technophysics Vidyasagar University, Midnapore – 721102, INDIA. E-mail: suva\_physics@yahoo.com, paultapas.phy1@gmail.com, rrpal@mail.vidyasagar.ac.in\* \*Corresponding Author

Received 15 September 2017; accepted 3 November 2017

### ABSTRACT

In this article, we present a new method of realization of a four-quadrant analog multiplier using operational amplifiers (OP-AMPs) and MOSFETs. The realisation is based on the quadric nature of current of MOSFET operating in triode region. The multiplier can be derived from the proposed configuration with using either bipolar or complementary metal-oxide-semiconductor (CMOS) OP-AMPs. It can be used effectively with a wide range of supply voltages down to  $\pm 1$  V and can multiply over the full scale of the supply voltage if the OP-AMPs used are rail-to-rail low voltage OP-AMPs. The performances of the proposed multiplier are tested through PSPICE (Cadence 16.6) simulation using TSMC 0.35  $\mu$ m CMOS process parameters and are found to be in close agreement with the theoretical predictions. Simulation results of the derived multiplier demonstrate a – 3 dB bandwidth of 9.6 MHz, a THD less than 1.21%, and an output referred noise less than 14 nV/ $\sqrt{}$ Hz at 1 k $\Omega$  load condition. The maximum power consumption of the circuit is 0.75 mW. The applications of the proposed multiplier are also included.

*Keywords:* Four-Quadrant Analog Multiplier, Operational Amplifier (OP-AMP), Amplitude Modulator (AM), Squarer Circuit, Frequency Doubler.

#### **1. Introduction**

Four-Quadrant analog multiplier is a key element in the field of analog signal processing, telecommunications and electronic systems. Modulation, demodulation, rectification, frequency translation, automatic gain control (AGC), squaring and square rooting of signals etc., are usually performed using this circuit [1-2]. There are different approaches to implement analog multiplier, such as, using modified Gilbert cell [3], based on trans-linear property of bipolar junction transistors or MOSFETs operating in saturation region [4-7], using switched-capacitor [8] and based on current-voltage characteristics of MOSFETs in triode-region [9]. But, these approaches are realised for the specific purpose and are not available in commercial integrated circuit (IC) form. Many circuit designers use different high-performance active building blocks (ABBs), namely, second generation current conveyor (CCII) [1], current controlled current conveyors (CCCII)

[10], operational trans-conductance amplifiers (OTA) [11], operational trans-resistance amplifiers (OTRA) [12], differential difference current conveyors (DDCC) [13], current differencing buffered amplifiers (CDBA) [14, 15], current controlled current differencing buffer amplifiers (CCCDBA) [16], current controllable current conveyor trans-conductance amplifiers (CCCCTA) [17], current differencing trans-conductance amplifiers (CCCTA) [17], current differencing trans-conductance amplifiers (CCCDTA) [18], current controlled current differencing trans-conductance amplifiers (CCCDTA) [2], etc., to make their multiplier circuits. But those circuits are costly. In the design of an electronic circuit, we also think of its economical aspect, along with its flexibility of design.

On the other hand, an operational amplifier (OP-AMP) is a commercially available, low-cost and high performance device and it is usually used as a basic circuit building block in analog circuits and system applications. The use of OP-AMP in the realisation of the analog multiplier will provide the structure of high performance at low cost and simple configuration. From literature survey, it is found that a no of implementations of OP-AMP based multiplier circuits have been reported [19-24]. However, careful observed study shows that those circuits are not free from limitations. The circuit reported in [19] uses as much as five OP-AMPs and eleven resistors. Using three OP-AMPs, Petchmaneelumka et al., presented an analog multiplier circuit reported in [20] but the circuit needed eighteen resistors. The circuit informed by Riewruja and Rerkratn [21] uses three OP-AMPs and sixteen resistors. The multiplier/divider circuits reported in [22] and [23] employ a single OP-AMP and eight MOSFETs but both positive and negative feedback are used in the circuits, thereby hampering the stability of the circuits. In [24] Ismail et al., introduced a multiplier/divider circuit using two OP-AMPs and six MOSFETs but the circuit used a sufficiently large supply voltage of  $\pm 6$  V.

In this paper, a new method of realization of a four-quadrant analog multiplier using operational amplifiers (OP-AMPs) is described. The proposed circuit employs three OP-AMPs, two MOSFETs and six resistors only. The realisation is based on the quadric nature of current of MOSFET operating in linear region. Both the bipolar and CMOS OP-AMPs can be used to realise the four-quadrant analog multiplication using the proposed structure. The proposed circuit provides low cost, simple configuration and good performance. The other important advantages of this circuit are as follows - it can be used with a wide range of supply voltages even from  $\pm 1$  V and it can multiply over the full scale of the supply voltage if the OP-AMPs used are rail-to-rail low voltage OP-AMPs. The workability of the derived multiplier is verified by PSPICE (Cadence 16.6) simulation using 0.35  $\mu$ m TSMC CMOS process parameters. It is found that the simulated results are in close agreement with the mathematically predicted results. The performances of the circuit as amplitude modulator, squarer and frequency doubler are also tested.

#### 2. Circuit description

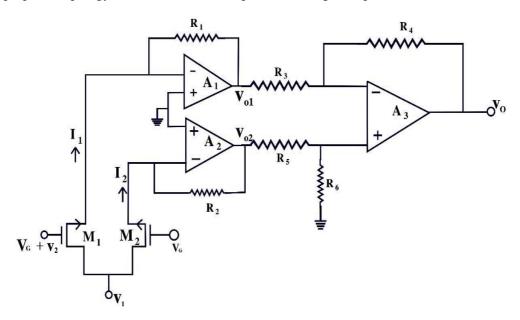

The proposed four-quadrant analog multiplier circuit is shown in Figure 1. The OP-AMPs  $A_1$  and  $A_2$  are assumed to be well matched such that the quiescent current and the bias current of the OP-AMPs are equal. The MOSFETs  $M_1$  and  $M_2$  are also assumed to be matched and biased to operate in triode region. Thus the expression for drain current for the MOSFETs is given by [12]:

A New Method of Realization of ...using Operational Amplifiers and MOSFETs

$$I_{d} = K \frac{W}{L} \left[ \left( V_{gs} - V_{t} \right) V_{ds} - \frac{V_{ds}^{2}}{2} \right]$$

(1)

where K is trans-conductance; W and L are the channel width and length of the MOSFET respectively. The other terms are of their usual meaning.

Since the source terminals of the MOSFETs  $M_1$  and  $M_2$  are virtually ground, thus using equation (1), the current  $I_1$  and  $I_2$  can be expressed as:

$$I_{1} = K \frac{W}{L} \left[ (V_{G} + v_{2} - V_{t})v_{1} - \frac{v_{1}^{2}}{2} \right]$$

(2)

$$I_{2} = K \frac{W}{L} \left[ (V_{G} - V_{t}) v_{1} - \frac{v_{1}^{2}}{2} \right]$$

(3)

If we assume  $R_1 = R_2 = R$ , then the output voltage of the OP-AMPs  $A_1$  and  $A_2$  i.e.  $v_{01}$  and  $v_{02}$  can be expressed as:

$$\mathbf{v}_{01} = -RK\frac{W}{L}\left[(V_{G} + \mathbf{v}_{2} - V_{t})\mathbf{v}_{1} - \frac{\mathbf{v}_{1}^{2}}{2}\right]$$

(4)

$$v_{02} = -RK \frac{W}{L} \left[ (V_{G} - V_{t})v_{1} - \frac{v_{1}^{2}}{2} \right]$$

(5)

The OP-AMP  $A_3$  along with resistors  $R_3-R_6$  form a differential amplifier, where  $R_3 = R_5 = R_i$ , and  $R_4 = R_6 = R_f$ . The routine circuit analysis shows that the output voltage of the proposed circuit can be expressed as:

$$\mathbf{v}_0 = \mathbf{K} \frac{\mathbf{W}}{\mathbf{L}} \left( \frac{\mathbf{R}\mathbf{R}_f}{\mathbf{R}_i} \right) (\mathbf{v}_1 \mathbf{v}_2) = \mathbf{K}_m(\mathbf{v}_1 \mathbf{v}_2) \tag{6}$$

where  $K_m = K \frac{W}{L} \left(\frac{RR_f}{R_i}\right)$ , is the multiplication gain. From equation (6), it is seen that the proposed topology can be used as a four-quadrant analog multiplier.

Figure 1. The proposed four-quadrant analog multiplier circuit.

### 3. Simulation results

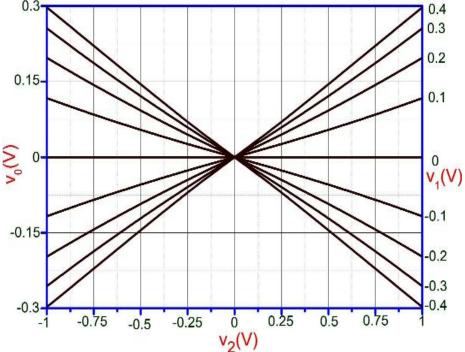

Although the proposed circuit can be derived from either bipolar or CMOS OP-AMPs and it can be used effectively with a wide range of supply voltages down to  $\pm 1$  V, but for the space convenience, in this article, we demonstrate only the simulation results of the proposed circuit, constructed by using the OP-AMPs, as in [25] with supply voltage  $\pm 1$  V. The resistors used in the circuit are chosen as  $R_1 = R_2 = R_3 = R_4 = R_5 = R_6 = 1$  k $\Omega$ with 1% tolerance and the transistors  $M_1$ - $M_2$  are used with aspect ratios having  $W/L = 2.8\mu/0.35\mu$ . Control voltage V<sub>G</sub> is taken as 1 V. TSMC 0.35  $\mu$ m CMOS model parameters are used for the simulation purpose. Figure 2 depicts the dc transfer characteristics of the proposed circuit as multiplier. Here, the input voltage v<sub>2</sub> is swept from -1 V to + 1 V while v<sub>1</sub> is varied from - 400 mV to + 400 mV in steps of 100 mV. It confirms that the proposed circuit acts as a four quadrant multiplier.

**Figure 2.** DC transfer characteristic ( $v_2$  is swept,  $v_1$  changed in steps).

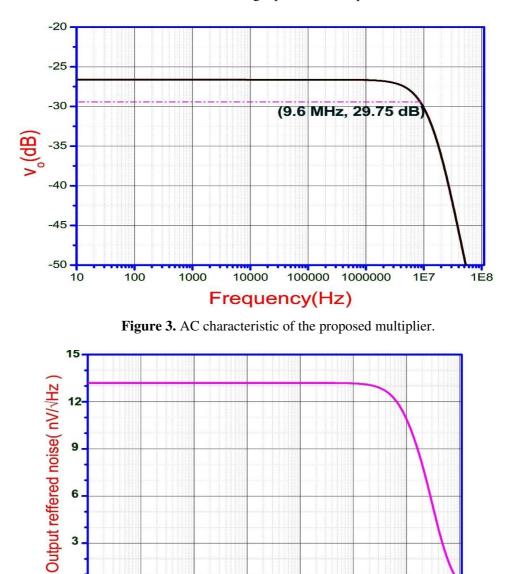

Figure 3 shows the frequency response characteristic of the proposed multiplier. In this case, voltage  $v_2$  is kept constant at 200 mV while  $v_1$  is taken as an AC source having amplitude 250 mV. The – 3 dB bandwidth is found to be about 9.6 MHz. Figure 4 shows the output referred noise voltage. It is found to be less than 14 nV/ $\sqrt{Hz}$  at 1 k $\Omega$  load condition.

A New Method of Realization of ...using Operational Amplifiers and MOSFETs

Figure 4. The output referred noise spectral density of the multiplier output at  $1K\Omega$  load condition.

Frequency(Hz)

10000

100000 1000000

1E7

1**E**8

1000

100

0

10

Figure 5 shows the variation of total harmonic distortion (THD) with respect to the variation of amplitude of the input signal with frequency (1 kHz, 10 kHz and 50 kHz) as a parameter. For this purpose a sinusoidal signal of varying amplitude with frequency 1 kHz/ 10 kHz / 50 kHz is taken as  $v_1$  where a constant 200 mV DC voltage is applied to  $v_2$ . It shows that the maximum THD does not exceed 1.21% for the entire input range.

Total power consumption of the proposed multiplier circuit is 0.75 mW when  $v_1 = v_2 = 0 V.$

Input voltage v<sub>1</sub>(mV)

250

300

350

400

450

# 4. Application example

# 4.1. Amplitude modulator

0.6

0.4

0.2

0

50

100

150

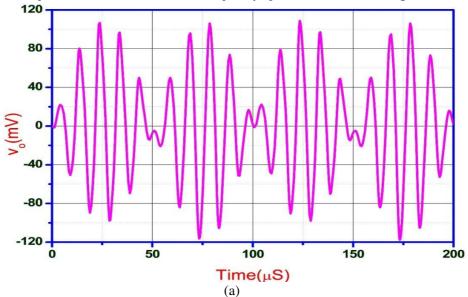

The proposed multiplier circuit, being four-quadrant multiplier, can be used as an amplitude modulator (AM). To verify the operation of the proposed configuration as a modulator, a 10 kHz signal with 300 mV amplitude is multiplied by 500 mV, 100 kHz signal. Figure 6 confirms about the modulation function. Figure 6(a) shows the time domain response of the modulator. The frequency spectrum is shown in Figure 6(b).

200

A New Method of Realization of ...using Operational Amplifiers and MOSFETs

Figure 6. Simulation result of the reported configurations as an amplitude modulator (a) time domain response (b) frequency spectrum.

## 4.2. Squarer

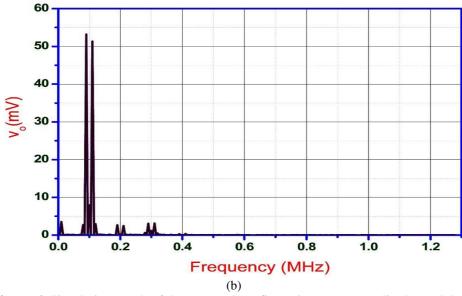

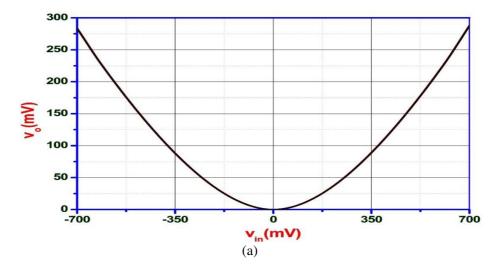

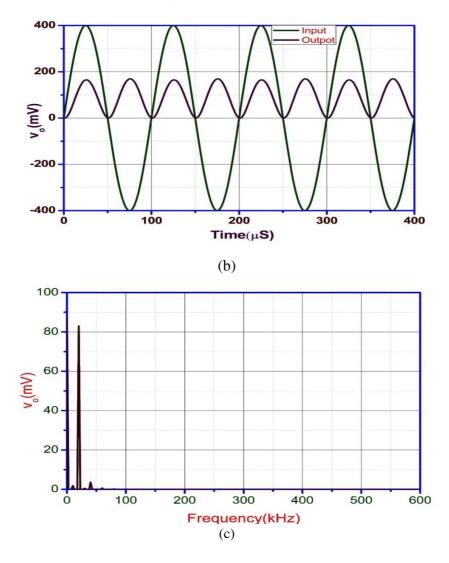

The proposed circuit can also be used as a squarer circuit if we take  $v_1 = v_2 = v_{in}$ . Figure 7(a) displays the square transfer characteristics of the reported configuration where  $v_{in}$  is varied from -700 mV to + 700 mV. The observed input and output of the squarer is shown in Figure 7(b) and the spectrum of the squared output is shown in Figure 7(c) when the input signal is taken as a 400 mV, 10 kHz sinusoid.

**Figure 7.** Simulation results of the proposed cell as a squarer (a) transfer characteristics (b) time response (c) frequency spectrum.

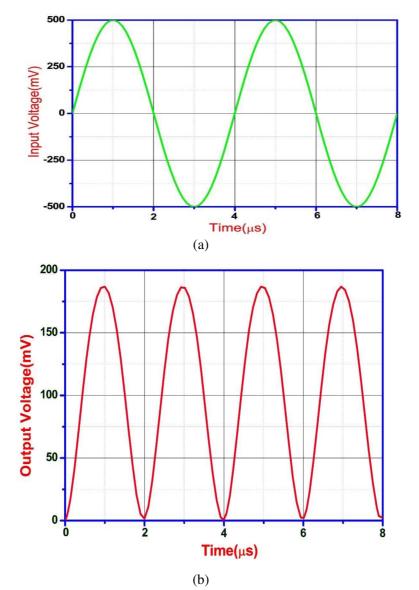

### 4.3. Frequency doubler

Being a four-quadrant multiplier, the proposed circuit can be used as a frequency doubler. Figure 8 shows that when a 500 mV, 250 kHz sinusoidal signal is used as input signal we get a 187 mV, 500 kHz signal at the output. Thus we may conclude that the proposed circuit can be efficiently used as a frequency doubler.

A New Method of Realization of ...using Operational Amplifiers and MOSFETs

Figure 8. Simulation result of the reported configurations as a frequency doubler (a) input (b) output.

### 5. Conclusion

An OP-AMP based four-quadrant analog multiplier circuit has been proposed. Both the bipolar and CMOS OP-AMPs can be used to realise the four-quadrant analog multiplication using the proposed structure. It provides low cost, simple configuration and good performance. It has been investigated that the proposed circuit can operate with a wide range of supply voltages down to  $\pm 1$  V and can multiply over the full scale of the supply voltage if the OP-AMPs used are rail-to-rail low voltage OP-AMPs. The performances of the derived multiplier are verified by PSPICE simulation results.

Simulation results show a THD less than 1.21%, a – 3 dB bandwidth of 9.6 MHz, an output referred noise less than 14 nV/ $\sqrt{Hz}$ , and a maximum power dissipation of 0.75 mW for the proposed circuit. The workability of the proposed circuits as amplitude modulator, squarer and frequency doubler are also described.

#### Acknowledgements

The authors would like to acknowledge Special Assistance Programme-University Grants Commission, India and FIST-Department of Science and Technology, India for their constant financial assistance to Department of Physics and Technophysics of Vidyasagar University.

### REFERENCES

- 1. C.Premont, N.Abouchi, R.Grisel and J.Chante, A BiCMOS current conveyor based four-quadrant analog multiplier, *Analog Integrated Circuits and Signal Processing*, 19 (1999) 159-162.

- 2. M.Siripruchyanun and W.Jaikla, A current-mode analog multiplier/divider based on CCCDTA, *Int. J. Electron. Commun. (AEÜ)*, 62 (2008) 223–227.

- 3. J.N.Babanezhad and G.C.Temes, A 20-V four-quadrant CMOS analog multiplier, *IEEE J. Solid-State Circuits*, 20 (1985) 1158-1168.

- 4. J.H.Huijsing, P.Lucas and B.D.Bruin, Monolithic analog multiplier-divider, *IEEE Journal of Solid-State Circuits*, 17 (1982) 9-15.

- 5. O.Oliaei and P.Loumeau, Four-quadrant class AB CMOS current multiplier, *Electronics Letters*, 32 (1996) 2327–2329.

- 6. A.Ravindran, K.Ramarao, E.Vidal and M.Ismail, Compact low voltage four quadrant CMOS current multiplier, *Electronics Letters*, 37 (2001) 1428–1429.

- 7. C.A.De La Cruz-Blas, A.J.L.Martin and A.Carlosena, 1.5 V four-quardarnt CMOS current multiplier/divider, *Electronics Letters*, 39 (2003) 434–436.

- 8. M.Yasumato and T.Enomoto, Integrated MOS four-quadrant analog multiplier using switched capacitor technique, *Electronics Letters*, 18 (1982) 769-771.

- C.Abel, S.Sakurai, E.Larsen and M.Ismail, Four-quadrant CMOS/BiCMOS multipliers using linear-region MOS transistors, *IEEE International Symposium* on Circuits and Systems, 5 (1994) 273–276.

- 10. E.Yuce, Design of simple current-mode multiplier topology using a single CCCII+, *IEEE Transaction on Instrumentation and Measurement*, 57 (2008) 631-637.

- 11. K.Kaewdang, C.Fongsamut and W.Surakampontorn, A wide band current-mode OTA based analog multiplier-divider, *Proceedings of the 2003 International Symposium on Circuits and Systems*, 1 (2003) 349-352.

- R.Pandey, N.Pandey, B.Sriram and S.K.Paul, Single OTRA based analog multiplier and its applications, *International Scholarly Research Network*, 2012 (2012) 1-7.

- H.O.Elwan and A.M.Soliman, CMOS differential current conveyors and applications for analog VLSI, *Analog Integrated Circuits and Signal Processing*, 11 (1996) 35–45.

- A New Method of Realization of ...using Operational Amplifiers and MOSFETs

- 14. A.U.Keskin, A four quadrant analog multiplier employing single CDBA, *Analog Integrated Circuits and Signal processing*, 40 (2004) 99-101.

- 15. J.K.Pathak, A.K.Singh and R.Senani, New Multiplier/Divider using a single Cdba, *American Journal of Electrical and Electronic Engineering*, 2 (2014) 98-102.

- 16. W.Jaikla and M.Siripruchyanun, Novel current mode four quadrant multiplier/divider based on current controlled CDBAs (CCCDBAs), *ECTI International Conference*, (2006) 509-512.

- 17. N.Sripanya, J.Kumbun, W.Jaikla and M.Siripruchyanun, A versatile analog multiplier/divider based on only single CCCCTA, *International Workshop and Symposium on science and technology 2008 Conference (I-SEEC 2008)*, (2008) 174-178.

- W.Tangsrirat, T.Pukkalanun, P.Mongkolwai and W.Surakampontorn, Simple current-mode analog multiplier, divider, square-rooter and squarer based on CDTAs, *International Journal of Electronics*, 65 (2011) 198-203.

- 19. V.Riewruja and A.Rerkratn, Four-quadrant analogue multiplier using operational amplifier, *International Journal of Electronics*, 98 (2011) 459-474.

- W.Petchmaneelumka, K.Songsataya, V.Riewruja and P.Julsereewong, Analog multiplier using operational amplifier, (<u>http://2005.iccas.org/submission/paper/upload/2multiplier.pdf</u>).

- 21. V.Riewruja and A.Rerkratn, Analog multiplier using operational amplifiers, *Indian Journal of Pure & Applied Physics*, 48 (2010) 67-70.

- 22. N.I.Khachab and M.Ismail, MOS multiplier/divider cell for analogue VLSI, *Electronics Letters*, 25 (1989) 1550-1551.

- 23. N.I.Khachab, A nonlinear CMOS analog cell for VLSI signal and information processing, *IEEE Journal of Solid State Circuits*, 26 (1991) 1689-1699.

- 24. M.Ismail, R.Brannen, S.Takagi, N.Fujii, N.I.Khachab, R.Khan and O.Asserud, Configurable CMOS multiplier/divider circuits for analog VLSI, *Analog Integrated Circuits and Signal Processing*, 5 (1994) 219-234.

- 25. S.Maiti and R.R.Pal, Low voltage high performance CMOS operational amplifier with rail-to-rail input/output stage, *Journal of Electron Devices*, 10 (2011) 483-488.